Cross-Layer and Multi-Objective Programming Approach for Next Generation Heterogeneous Parallel Computing Systems

Project Number 688146

# D3.1 – First report on programmer- and productivityoriented software tools

Version 2.0 2 November 2017 Final

**Public Distribution**

# Unparallel Innovation, Wings ICT Solutions, Easy Global Market, University of Stuttgart

Project Partners: Easy Global Market, GMV, Intecs, The Open Group, University of Stuttgart, University of York, Unparallel Innovation, WINGS ICT Solutions

Every effort has been made to ensure that all statements and information contained herein are accurate, however the PHANTOM Project Partners accept no liability for any error or omission in the same.

© 2017 Copyright in this document remains vested in the PHANTOM Project Partners.

# **PROJECT PARTNER CONTACT INFORMATION**

| Easy Global Market                      | GMV                                    |

|-----------------------------------------|----------------------------------------|

| Philippe Cousin                         | José Neves                             |

| 2000 Route des Lucioles                 | Av. D. João II, Nº 43                  |

| Les Algorithmes Batiment A              | Torre Fernão de Magalhães, 7º          |

| 06901 Sophia Antipolis                  | 1998 - 025 Lisbon                      |

| France                                  | Portugal                               |

| Tel: +33 6804 79513                     | Tel. +351 21 382 93 66                 |

| E-mail: philippe.cousin@eglobalmark.com | E-mail: jose.neves@gmv.com             |

| Intecs                                  | <b>The Open Group</b>                  |

| Silvia Mazzini                          | Scott Hansen                           |

| Via Umberto Forti 5                     | Rond Point Schuman 6                   |

| Loc. Montacchiello                      | 5 <sup>th</sup> Floor                  |

| 56121 Pisa                              | 1040 Brussels                          |

| Italy                                   | Belgium                                |

| Phone: +39 050 9657 513                 | Tel: +32 2 675 1136                    |

| E-mail: silvia.mazzini@intecs.it        | E-mail: s.hansen@opengroup.org         |

| University of Stuttgart                 | University of York                     |

| Bastian Koller                          | Neil Audsley                           |

| Nobelstrasse 19                         | Deramore Lane                          |

| 70569 Stuttgart                         | York YO10 5GH                          |

| Germany                                 | United Kingdom                         |

| Tel: +49 711 68565891                   | Tel: +44 1904 325571                   |

| E-mail: koller@hlrs.de                  | E-mail: neil.audsley@cs.york.ac.uk     |

| Unparallel Innovation                   | WINGS ICT Solutions                    |

| Bruno Almeida                           | Panagiotis Vlacheas                    |

| Rua das Lendas Algarvias, Lote 123      | 336 Syggrou Avenue                     |

| 8500-794 Portimão                       | 17673 Athens                           |

| Portugal                                | Greece                                 |

| Tel: +351 282 485052                    | Tel: +30 211 012 5223                  |

| E-mail: bruno.almeida@unparallel.pt     | E-mail: panvlah@wings-ict-solutions.eu |

# **DOCUMENT CONTROL**

| Version | Status                                                              | Date     |

|---------|---------------------------------------------------------------------|----------|

| 0.1     | Definition of TOC                                                   | 12/04/17 |

|         | Contribution of WINGS to Parallelization Toolset and Programming    | 05/05/17 |

| 0.2     | Interface                                                           |          |

| 0.3     | Contribution of EGM to Model Based Testing section                  | 09/05/17 |

| 0.4     | Update of WINGS' and EGM's contributions                            | 25/05/17 |

| 0.5     | Contribution of HLRS to Phantom Application Parallelization Ap-     | 30/5/17  |

|         | proach and of YORK to FPGA section on the parallelization toolset   |          |

| 0.6     | Executive Summary, Introduction and Conclusion                      | 31/5/17  |

| 0.7     | HLRS and York review and corresponding modifications                | 7/6/17   |

| 1.0     | Final Contributions and Modifications                               | 9/6/17   |

| 2.0     | Contributions from WINGS, EGM, YORK and UNPARALLEL of               | 2/11/17  |

|         | the Innovations Beyond the State-of-the-Art subsections to incorpo- |          |

|         | rate EC reviewers' comments.                                        |          |

# TABLE OF CONTENTS

| 1. Introduction                                                                                                                                          | 1                    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| 1.1 Scope                                                                                                                                                | 1                    |

| 1.2 PHANTOM Application Parallelization Approach                                                                                                         | 2                    |

| 2. Parallelization Toolset                                                                                                                               |                      |

| 2.1 Use Case requirements                                                                                                                                | 4                    |

| <ul><li>2.2 Code Analysis</li><li>2.2.1 Design Specifications</li><li>2.2.2 Implementation Details</li></ul>                                             | 4                    |

| <ul><li>2.2.3 Demonstration/Example usage</li><li>2.2.4 Dependencies/integration aspects</li><li>2.2.5 Innovations beyond the state-of-the-art</li></ul> | 9                    |

| <ul> <li>2.3 Technique Selection</li></ul>                                                                                                               | 11<br>12<br>15<br>16 |

| <ul> <li>2.4 FPGAs</li> <li>2.4.1 PHANTOM Hardware Interface</li> <li>2.4.2 Innovations beyond the state-of-the-art</li> </ul>                           | 20<br>20             |

| 3. Programming Interfaces                                                                                                                                |                      |

| 3.1 Use Case requirements                                                                                                                                | 23                   |

| <ul><li>3.2 Shared Memory API</li><li>3.2.1 Design Specifications</li><li>3.2.2 Implementation Details</li></ul>                                         | 24                   |

| <ul><li>3.3 Queue API</li><li>3.3.1 Design Specifications</li><li>3.3.2 Implementation Details</li></ul>                                                 | 26                   |

| <ul><li>3.4 Signal API</li><li>3.4.1 Design Specifications</li><li>3.4.2 Implementation Details</li></ul>                                                | 29                   |

| <ul><li>3.5 PHANTOM API for CPU-GPU communication</li></ul>                                                                                              | 32                   |

| 3.6 Dependencies/integration                                                                                                                             | 35                   |

| 3.7 demonstrator/Example usage                                                                                                                           | 35                   |

| <ul> <li>3.8 Innovations beyond the state-of-the-art</li></ul>                                                                                           |                      |

| 4. Model Based Testing                                                                                                                                   |                      |

| 4.1 Use Case requirements                                                                                                                                |                      |

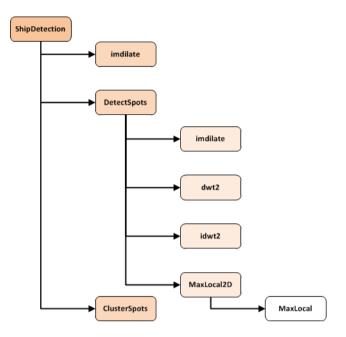

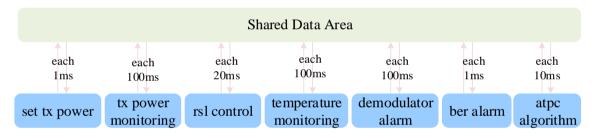

| 4.1.1 Surveillance specification                       | 40 |

|--------------------------------------------------------|----|

| 4.1.2 Telecom specification                            |    |

| 4.1.3 HPC specification                                |    |

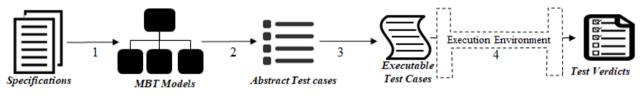

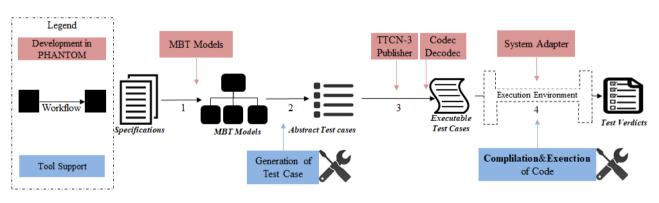

| 4.2 Design Specifications                              | 44 |

| 4.3 Implementation Details                             |    |

| 4.3.1 MBT models                                       |    |

| 4.3.2 Generated Test cases                             |    |

| 4.3.3 TTCN-3 Publisher                                 |    |

| 4.3.4 Codec/Decodec                                    |    |

| 4.3.5 System Adapter                                   |    |

| 4.3.1 Implementation Summary                           |    |

| 4.4 Demonstration and Testing Results                  | 55 |

| 4.5 Dependencies/integration                           |    |

| 4.5.1 Integration objectives                           |    |

| 4.5.2 PHANTOM platform interfaces                      |    |

| 4.5.3 MBT interaction flow with PHANTOM                |    |

| 4.6 Innovations beyond the state-of-the-art (EGM)      |    |

| 4.6.1 Background technologies utilised in development  |    |

| 4.6.2 Summary of new technologies/extensions developed | 61 |

| 4.6.3 Early/Full Prototypes functionality              |    |

| 5. Conclusion                                          | 64 |

| 6. References                                          |    |

|                                                        |    |

# **EXECUTIVE SUMMARY**

This document describes the initial developments on the tools and technologies to support the activities of the Parallelization Toolset and Model Based Testing modules of the PHANTOM architecture, and on the specification of the PHANTOM Programming Interface. Further developments will be reported in D3.2 – "Final report on programmer- and productivity-oriented software tools".

In section 2, the Parallelization Toolset is described. Presented in this section are the technologies and algorithms for both code analysis and technique selection. Code analysis uses tools like ANTLR and CETUS to parse and to identify parallelisable code. This section also describes the methodology used to select the proper technology for the implementation of parallelised tasks based on the deployment plan provided by the Multi-Objective Mapper. The PHANTOM API is implemented by either CUDA, OpenMP, OpenCL, MPI or Pthreads APIs, based on these decisions. Still in the context of the Parallelization toolset, it is also provided some insight on the work developed for task parallelization on FPGAs.

Section 3 identifies and describes APIs to support the development of PHANTOM applications following a component-based approach. These APIs use the C programming language and allow the use of generic parallelisation functionalities, addressing both synchronization and data sharing mechanisms. This section also presents the PHANTOM API for communications between CPUs and the attached GPU devices, used to describe functions intended to be executed in GPU devices.

The final section reports the current status of Model Based Testing development. A study of the functional behaviour of each use case is performed to understand the expected inputs and outputs of the tests. A methodology for the definition and execution of tests is provided, being also identified the tools to be used in PHANTOM and how the Model Based Testing module will interact with other modules of PHANTOM architecture.

# **1. INTRODUCTION**

### **1.1 SCOPE**

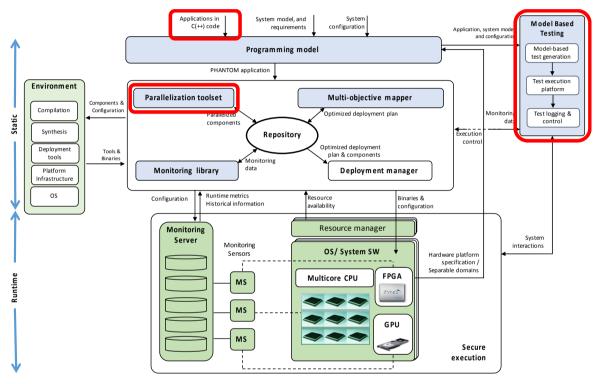

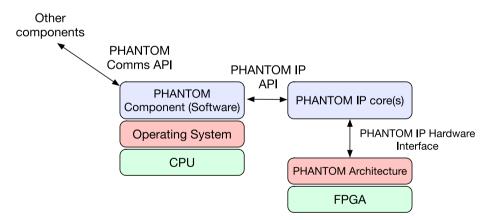

This document reports the progress of all tasks executed in the context of WP3 – "Programmer- and productivity- oriented software tools. Figure 1-1 shows a representation of the PHANTOM architecture. Highlighted in red are the components developed within the context of WP3 activities. These components are the PHANTOM Programming API, the Parallelization Toolset and the Model Based Testing.

Figure 1-1: Modules of the PHANTOM architecture addressed in WP3

The Parallelization Toolset, which will be discussed in section 2, identifies parallelizable sections of the PHANTOM components, provides them to the Multi-objective Mapper and, if the mapper elects to use a parallelisation scheme for that component, implements it.

The PHANTOM Programming Interface details and implements the communication and data sharing between the different components that compose a PHANTOM application. This is described in section 3.

Model Based Testing corresponds to a toolset dedicated to performing the testing of the PHANTOM application, both helping developers to test the functional behaviour of the application and providing metrics to help the Multi-objective Mapper on the decision of parallelization plan. This component will be described in section 4.

# **1.2 PHANTOM APPLICATION PARALLELIZATION APPROACH**

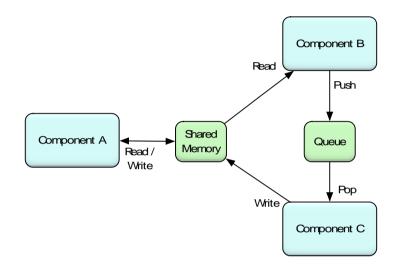

The PHANTOM programming model for applications (see D2.1 for details) follows a component-based approach – the application is constructed as a set of individual components (Figure 1-2). Components have their own thread(s) of control and are independent. They do not share data or communicate, except where explicitly enumerated by the design of the application. The enumeration of components and their shared data is called the Component Network.

Figure 1-2: Component-based PHANTOM application

The components are separate processes and can thus benefit from deployment on distributed hardware resources (see D4.2 for details on the PHANTOM heterogeneous infrastructure testbed). The programming model provides the notion of communication channels, through which the components must communicate with one another in order to exchange the data or synchronise the execution (such as a one-directional "queue" or bidirectional "shared", see more in D2.1).

Since the PHANTOM programs are running on different hardware and thus do not share any common compute resources, they can be treated as fully parallel executions. In order to synchronise the execution of application components in accordance with the application logic, the programs might use sync messages (which are enumerated in the Component Network).

The component-based execution constitutes a basic level of parallelism – coarsegrained. Coarse-grained parallelism depends on the application logic and is enforced by the application developer through the programming model (and the associated execution environment of the PHANTOM platform).

The next parallelisation level – fine-grained parallelism – can be achieved inside the individual components and aims to fully utilize the available parallel compute power (such as CPU cores, GPU kernels, or FPGAs). Fine-grained parallelism requires a special framework – the Parallelization Toolset.

# 2. PARALLELIZATION TOOLSET

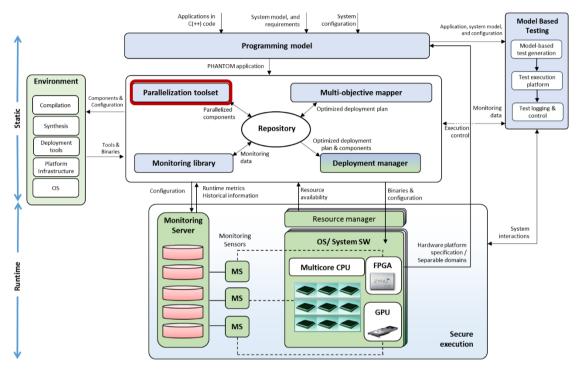

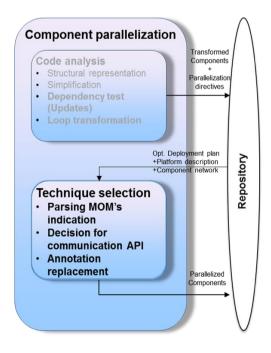

The Parallelisation Toolset is responsible for the identification of concurrent regions in the application code, for source-to-source code transformation to implement parallelisation, and for considering pre-specified requirements and the decision of the Multi-Objective Mapper described in D2.1.

Figure 2-1: Parallelization Toolset positioning in PHANTOM toolflow.

Since PHANTOM uses a component based programming model (as described in D1.2), the Parallelisation Toolset retrieves the components which compose the PHANTOM program, analyses and transforms them in order to 1) replicate them to many identical copies that run on different 'slices' of input data and 2) to create different versions of components which exploit GPUs, FPGAs, SMP multiprocessors or Cloud environments. The first operation is performed by the Code Analysis described in section 2.2, which provides appropriate parallelization information to the Multi-Objective Mapper. Then the latter functionality is performed by Technique Selection (described in section 2.3), driven by the mapping decision of the Multi-Objective Mapper and assisted by four sub-toolsets, which process the components towards a specific platform architecture. The sub-toolsets consist of:

- CPU Toolset (CT) for transforming components targeting shared memory uniform memory access (UMA) or non-uniform memory access (NUMA), cache coherent, symmetric multiprocessing (SMP), CPU architectures

- GPU Toolset (GT) which transforms components for graphics processing units (GPU) implementation

- FPGA Toolset (FT), handling components for FPGA implementations

- Cloud Technologies Toolset (CTT): Transforms components for Cloud environments

This document primarily considers the CPU Toolset and GPU Toolset, whilst the rest of the sub-toolsets will be described in future deliverables of WP3 and WP4.

# 2.1 USE CASE REQUIREMENTS

The Parallelisation Toolset is one of the main components of PHANTOM framework and it will transform and generate parallel code for the heterogeneous platforms that comprise the infrastructure of PHANTOM. Its operation is therefore significant for all three use cases: Surveillance, Telecommunications and High-Performance Computing. In general, the use case requirements refer to the support and the capabilities of code generation, support of heterogeneous platforms, support of parallelisation APIs and programming languages, as defined in D1.1. The addressed requirements are the following:

| Req. No. | Requirement                                                                                                                                                | <b>Overall Priority</b> |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| U3       | Parallelization of sequential application code, when complemented<br>by parallelization instructions provided by the user                                  | SHALL                   |

| U4       | Automatic identification and parallelization of regions of sequential application code                                                                     | SHOULD                  |

| U5       | Support for multi-threaded concurrent tasks, including communica-<br>tion and synchronisation                                                              | SHALL                   |

| U6       | Support of parallelization, influenced by non-functional require-<br>ments information                                                                     | SHOULD                  |

| U7       | Support for communications data-centric applications (e.g. automat-<br>ic scaling of components to the actual size of data to be processed)                | SHALL                   |

| U8       | Support for component-based application design                                                                                                             | SHALL                   |

| U14      | Exploitation of SIMD instructions sets provided by CPUs                                                                                                    | SHOULD                  |

| U19      | Generation of target dependent parallel code for all mandatory<br>target platforms without user involvement when sufficient annota-<br>tions are provided. | SHOULD                  |

| U21      | Automation of transferring data to/from different memories accord-<br>ing to the component data model                                                      | SHALL                   |

| U22      | Support for indication of application blocks to be parallelized                                                                                            | SHALL                   |

| U23      | Support for indication of data dependencies, defining how data can<br>be partitioned/split among the parallel application components                       | SHALL                   |

| U32      | Support for application source code developed in C                                                                                                         | SHALL                   |

| U33      | Support for higher level language such as Java and C++                                                                                                     | MAY                     |

| U37      | Support for exposing the generated parallel code to the user                                                                                               | SHALL                   |

| U38      | User modifications of the generated parallel code subject to re-<br>strictions or protected segments                                                       | SHOULD                  |

# 2.2 CODE ANALYSIS

The main task of the Code Analysis is to parse the components' source code of the user provided application and perform analysis for identifying the code's parallel regions, along with transformation, with emphasis on loop and task parallelization.

### 2.2.1 Design Specifications

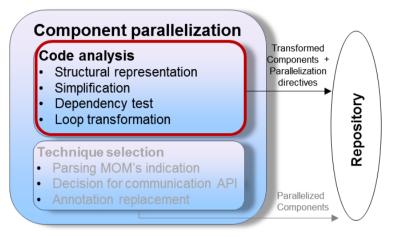

Code Analysis retrieves the Component Network (described in D1.2.) which is provided by the user and stored in the PHANTOM Repository. Code Analysis parses the Component Network in order to identify the user-provided components along with their source code, which are stored in the Repository. Then the tool performs its processing according to the workflow depicted in the following figure:

Figure 2-2: Code analysis positioning in PHANTOM tool-flow

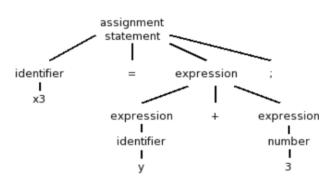

The first operation includes the creation of a structural representation (i.e. parse tree as depicted in Figure 2-3) of the source code of each component, which will facilitate the identification of the variables and functions, important for loop and task parallelization.

Figure 2-3: Example of source code structural (tree) representation.

Based on the structural representation, the analysis will attempt to further simplify the source code in order to further facilitate the loop and task parallelization. The code analysis is then performed by searching the simplified source code for data dependencies [10][11][12], that could prevent the components parallelization (using tools such as COINS [8], CETUS [9]). The next step is the identification of "for" loops and variables that can be parallelized, where the tool annotates them as parallelizable or not according to the dependency test outcome. In case a loop is parallelizable, the code analysis transforms the parallelizable loops-variables attributes (e.g. iteration size-limit) with specific PHANTOM directives (e.g. phantom\_slice\_size()) that enable the selected loop variables to be further parallelized and the component to be replicated.

Finally, the analysis exports the parallelization annotations/directives which provide the maximum number of possible parallel components to the Multi-Objective Mapper module (described in D2.1).

# 2.2.2 Implementation Details

The Code Analysis is a set of classes and functions implemented in Java, using appropriate XML libraries to be able to parse and modify XML documents. The input of the Code Analysis is the Component network XML document and the specified components' source codes (at the current stage C/C++) along with their header files that will be further analysed.

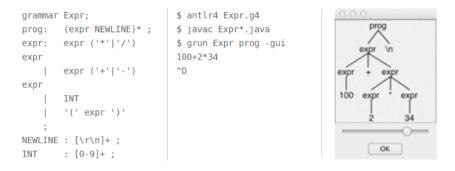

Then the Code Analysis uses ANTLR [1] (see also D4.1) tool to parse and create the structural (tree) representation of each identified component. An example of the ANTLR operation is provided in the following figure:

Figure 2-4: Example of ANTLR parsing. (Picture from ANTLR framework [1])

ANTLR stores the exported parse tree in a Java form that is aligned with the Java form of the Code Analysis and simplifies the following steps of the analysis.

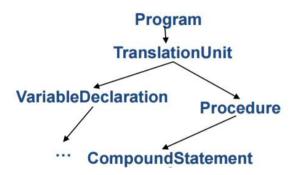

In order to achieve a more efficient analysis of the source code elements (declarations, expressions variables), Code Analysis employs the CETUS tool [9] (see also D4.1) in order to provide an intermediate representation between the parse tree and the source code, as shown in Figure 2-5, that will consist of the objects that are more meaningful for the parallelization process (e.g. for, while, loops, loop size, loop iterators, etc.).

Figure 2-5: Example of intermediate representation using CETUS [9]

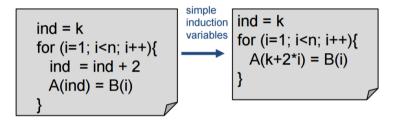

The next step consists of code simplification in which the Code Analysis attempts to transform the source code assignments and operations in a form that will facilitate the loop and task parallelization (e.g. simplifies mathematical operations). The Code Analysis is currently using CETUS functions for code simplification but also other refactoring tools are under investigation, such as CodeRush [3] and AutoRefactor [4]. Specifically, the Code Analysis will execute the single variable declaration function, which re-writes variable declaration to achieve single variable per declaration. Then it executes induction substitution which recognizes and substitutes induction variables in loops that take the form of iv = iv + expr [9]. Assignments of this form prevent a loop from being parallelized due to its data dependence, since variables inside a loop cycle depends on the values assigned in other cycles. The CETUS induction substitution will transform these assignments to a form that does not include significant data dependencies, thus enabling loop parallelization. This substitution process is exemplified in the following figure.

Figure 2-6: Example of code simplification

After the code simplification, the Code Analysis will perform one of the most significant tasks which is the identification of data dependencies [10][11][12]. As aforementioned, the Code Analysis will give emphasis on searching for loops that are parallelizable, since they consume most of the execution time of a sequential program. In case a loop includes dependencies between its instructions it cannot be parallelized without affecting its initial context and operation. These situations require the execution of code transformation to eliminate the data dependencies. The CETUS data dependence analysis framework [9] gathers dependence information for array accesses within loop nests and creates a data dependence graph, on top of which it performs conventional dependence tests, such as the Banerjee test [13][14] and the Greatest Common Divisor test [15]. In case that a loop includes data dependencies that cannot be resolved then the loop is characterized as not parallelizable. Some data dependencies can be resolved either by CETUS's conventional methods either by custom modifications and algorithms. The current version of Code Analysis extends the loop dependence handling by introducing a custom modification of the CETUS testing to enable loop transformation towards the PHANTOM parallelization requirements. For example, in case of a specific type of data dependence in a "for" loop that can be split by iteration size, the code analysis will slice the "for" loop in a multitude of "for" loops substituting the iteration size with the PHANTOM specific directive by (phantom\_slice\_size()), thus each component will execute the loop until the size of the each slice, as shown in Figure 2-7.

```

for (int i = 0; i < 1024; i++) {

output_sum[i] = data[i] *

(i+4) * (i-16);

}

for (int i = 0;

i < phantom_slice_size();

i++) {

output_sum[i]= data[i] *

(i+4) * (i-16);

}

</pre>

```

#### Figure 2-7 Example of a parallelizable loop

Data dependency test is an aspect that can improve loop parallelization and is investigated for the future versions of the Code Analysis. Since, PHANTOM addresses parallelisation of components targeting heterogeneous platforms, more data dependency algorithms will be investigated, considering also range analysis aspects for future versions.

The final step of the Code Analysis includes the exploitation of the achieved parallelization level of the analysed components. The analysis edits the Component Network XML document where, for each component, it adds the maximum number of possible parallel components (and communication objects accordingly), as described in the following figure:

```

<!-- Components Description -->

<component name="A" type="asynchronous">

<PT:parallelisation-directive max_number="64" name="subcomponents" set-by="PT"/>

```

### Figure 2-8: Example of parallelization directive

The above figure depicts an example of the XML element "parallelisation directive" which provides the maximum number of possible parallel subcomponents, for a specific component (in this case "component name='A'"). This information will assist the Multi-Objective Mapper module (described in D2.1) to further replicate the parallelizable components, improving the mapping outcome and overall efficiency.

### 2.2.3 Demonstration/Example usage

The Code Analysis is evaluated in terms of its ability to identify parallelizable loops in the source code of the user provided components. The current testing scenario consists of the following steps:

- 1. The Parallelization Toolset retrieves the component network from the repository

- 2. The Code Analysis parses the components specified in the component network

- 3. The identified loops are tested for data dependencies

- 4. The parallelizable loops are transformed accordingly, with the addition of PHANTOM specific directives

- 5. The Code Analysis exports the parallelization directives to the Component Network that will used by MOM.

The following picture provides a test run of the Code Analysis on a custom source component (in the C/C++ language), along with a Graphical User Interface that helps the user to execute the code analysis.

| WINGS ICT Solutions Ltd.                                                                                           |                                                                                                                                                         |   |                                                                                                                                            |  |

|--------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---|--------------------------------------------------------------------------------------------------------------------------------------------|--|

| alysis results                                                                                                     | Code comparison                                                                                                                                         |   |                                                                                                                                            |  |

| nalysis duration 4532ms                                                                                            | Initial code                                                                                                                                            |   | Analysis refinement                                                                                                                        |  |

| s<br>Component Detected loops Parallelisable Parallelisablon dire<br>A 1 1 64 max# compone<br>B 2 0 1 max# compone | /*************************************                                                                                                                  |   | /* CA */<br>#include "stdio.h"<br>typedef int bool;<br>int main(void )<br>/                                                                |  |

|                                                                                                                    | #define false 0<br>int main(void) {<br>int t;                                                                                                           |   | '<br>int i;<br>#pragma phantom signal in ready<br>bool ready;<br>#pragma phantom shared in input. data                                     |  |

| Add Delete                                                                                                         | #pragma phanhom signal in ready<br>bool ready;<br>#pragma phanhom shared in input_data<br>double input_data[64];                                        |   | double input_data[64];<br>#pragma phantom queue 0 out output_sum<br>double output_data[64];<br>/* double output_data[;*/<br>int_ret_val_0; |  |

| D FILE TO RE RUN CODE ANALYZER CLEAR                                                                               | #pragma phantom queue 0 out output_sum<br>double output_data[64];<br>//double output_data;                                                              | 0 | phantom_wait(( & ready));<br>phantom_synchronize(input_data);<br>/*                                                                        |  |

| t target filename application_ref4.xml                                                                             | <pre>phantom_wait(&amp;ready);<br/>phantom_synchronize(input_data);<br/>for(i = 0; i &lt; 64; i++) {<br/>output_data[]=input_data[]*(i+4)*(i-16);</pre> | ) | PHANTOM Comment Loop# 0 is-paralleltrue<br>for (i=0; i <phantom_slice_size; )<="" i++="" td=""></phantom_slice_size;>                      |  |

| nsole log<br>CA.c. nullLoop# 0 contains Loop carried dependency x0 and                                             | //output_data += input_data(i)*i/(i+2);<br>}<br>phantom_queue_put(output_data);                                                                         |   | output_data[i]=((input_data[i]*(i+4))*(i-16));<br>/* output_data += input_data[i]/(i+2); */<br>}<br>phantom_queue_put(output_data);        |  |

| can be parallelized using<br>PHANTOM loop transformation<br>contains Loop carried dependency x1 and                | }                                                                                                                                                       |   | return _ret_val_0;<br>}                                                                                                                    |  |

| can be parallelized using<br>PHANTOM loop transformation                                                           | #include "stdio.h"<br>typedef int bool:                                                                                                                 |   | /" CB */<br>#include "stdio.h"<br>typedef int bool;                                                                                        |  |

Figure 2-9: Example of Code Analysis test

In the example of the above, the analysis identified all existing loops and was able to parallelize one of them 64 times, whilst the remaining "for" loops could not be parallelized due to unresolved dependencies. Current results show that the first version of the Code Analysis is able to identify all existing loops inside the components' source code, and is able to resolve-parallelize a number of non-complex existing loops. The number and the complexity of the parallelized loops is expected to grow in the next versions of the Code Analysis. Furthermore, the Code Analysis is tested in terms of execution time since it might add a non-trivial overhead to the overall optimization and optimization process. Current results show that the execution time of the Code Analysis has values in the range of a few seconds (<10s) for up to 5 source code components, but more tests will follow in the future implementations.

# 2.2.4 Dependencies/integration aspects

The Code Analysis is related to the PHANTOM Programming Model (see D1.2), from which it retrieves the user defined Component Network, along with the application components' source code to be parallelized. Then, the Code Analysis transformation phase uses the PHANTOM Communication APIs, protocols and corresponding functions that will be added in the components' source code to provide the loop parallelization. Finally, the Code Analysis is strongly related to the Multi-Objective

Mapper (MOM) developed in WP2, since the analysis will provide the parallelization directives facilitating MOM to explore the available number of the parallelized components, in order to replicate them. Existing parallelization tools and frameworks will be investigated to facilitate the deployment of the parallel design regions, as suggested by WP1, on the heterogeneous infrastructure, set up by WP4.

### 2.2.5 Innovations beyond the state-of-the-art

# 2.2.5.1 Background technologies utilised in development XML Parsing Classes

The Code Analysis is a set of classes and functions implemented in Java, using appropriate XML libraries to parse and modify XML documents. These libraries are mainly required to process the Component Network that provides all necessary information about the components.

### Source code Parser

The Code Analysis uses the ANTLR tool (http://www.antlr.org/) to parse and create the structural (tree) representation of each identified component. ANTLR stores the exported parse tree in a Java form that is aligned with the Java form of the Code Analysis and simplifies the following steps of the analysis.

### Intermediate Representation (IR) and Dependence Analysis

CETUS compiler infrastructure (https://engineering.purdue.edu/Cetus/) is used for the IR and the Dependence Analysis of the components' code. The tool is responsible for both, creating an intermediate level of description for the code, and running some of the latest available dependence tests on it, determining if it's parallelizable or not.

# 2.2.5.2 Summary of new technologies/extensions developed High-Level Annotations and Parallelization Directives

Code Analysis was extended with certain functionalities designed to provide helpful information about the components' code. In specific, high level annotations are produced by analysing the results provided by CETUS, as well as directives about components parallelization capabilities are added in the component network, information that will be used for the functionality of the Multi-Objective Mapper.

# 2.2.5.3 Early/Full Prototypes functionality Early-First Year Prototype

The component model is being successfully extracted from the Component Network to be used by the rest of the Code Analysis' functionalities. The analysis of the components' code is able to employ successfully the CETUS compiler infrastructure and locate certain parts of the code that do not seem to have any dependencies, thus, can be parallelized. According to the information extracted by the Code Analysis, parallelization directives are successfully added to both the Component Network and to the source code of each component.

# **Full Prototype and Next Steps**

Driven by the continuous research that is being done on automatic parallelization, other tools are being compared with CETUS, with new techniques at their disposal and more capabilities. In specific, the ROSE Compiler has already been embedded in the PT and is currently being tested against CETUS with promising results, as well as PLUTO + Polly (with its use of the Polyhedral Model). In addition, other code analysis tools will also be investigated in the context of source code simplification and to further provide more facilities in code transformation and dependence analysis, in regard to the development of the latest parallelization techniques available.

# 2.3 **TECHNIQUE SELECTION**

The Technique Selection (TS) operation is performed after the execution of the Multi-Objective Mapper, in order to receive its mapping decision and produce the parallelization indications inside the components' source code, to guide the Deployment manager on the generation or activation of the actual parallelization functions.

# 2.3.1 Design Specifications

The Technique Selection receives the MOM outcome, indicating the mapping decisions, along with the platform description and the component network to further decide on the best parallelization API for the parallelization technique (e.g. OpenMP, threads communication, MPI, etc.). Furthermore, TS will provide information to the PHANTOM API execution management functions, developed in the context of PHANTOM to initialize/finalize important functionalities of low level communication APIs, applied to all components that will use those APIs (e.g. in case there are more than one pthread component these functions initialize mutex variables). These functions facilitate the Deployment Manager with the adoption and execution of low level communication APIs. TS functionalities are detailed in the following figure:

#### Figure 2-10: Techniques selection positioning in PHANTOM tool-flow

As depicted in the above figure (Figure 2-10) TS first parses the MOM's outcome (i.e. optimized deployment plan) in order to:

- 1. Classify the components depending on the type of platform to which they are mapped;

- 2. Identify the interacting components of the final deployment.

Then, the TS operation executes a fast and low complexity decision mechanism which selects the appropriate low-level communication API (e.g. OpenMP, MPI, OpenCL) that is the best fit for the components, according to the specified mapping to physical resources (processing elements).

Furthermore, TS provides information regarding the PT techniques selection by editing PHANTOM API functions with annotations that will facilitate the Deployment Manager operation based on existing parallelization APIs. For example, #pragma phantom MPI\_Send

In addition, the existing communication protocol annotations (e.g. #pragma phantom shared in data), are replaced by lower level communication directives (e.g. #pragma phantom MPI\_Send()), that indicate the Deployment manager to generate or activate the actual parallelization functions.

### **2.3.2** Implementation Details

The Technique Selection tool is implemented in Java and similarly to the Code Analysis it uses XML libraries to parse its input and generate its output. The input to TS is the Optimized Deployment Plan (in XML form) provided by the MOM, the Component Network XML document and the specified components' source codes (currently supporting C/C++) along with their header files that will be further analysed.

The first step of the operation includes the XML parsing and analysis of MOM's optimized deployment plan along with the XML parsing of the Component Network in order to correlate the information from the two documents. The current implementation considers the following component attributes:

| Component Attributes                    |

|-----------------------------------------|

| Mapping name: e.g.<br>component_A_1_map |

| Mapping type: e.g. processing           |

| Component name: e.g. A_1                |

| Component id: 1                         |

| Subcomponents: e.g. 32                  |

| Tahla 2-1. Com | ponent attributes | for Technic | uua Salaction |

|----------------|-------------------|-------------|---------------|

|                | poment attributes | TOT TECHNIC | ue selection  |

| Processor name: e.g. P1 |

|-------------------------|

| CPU-name: e.g. CPU2     |

| Device Type: CPU-based  |

The first attribute is the mapping name, relative to the name of the component. Then the mapping also includes a mapping type, which indicates whether the mapping refers to a mapping of a component to a processing element (tagged as "processing") or a mapping of a communication object (tagged as "communication") to a physical communication buffer. In addition, TS considers the component name, id and also the "Subcomponents" attribute, which refers to the possible number of parallel subcomponents of this component. TS considers the processor name, the CPU name and the Device Type (e.g. CPU-based) to which a component is mapped.

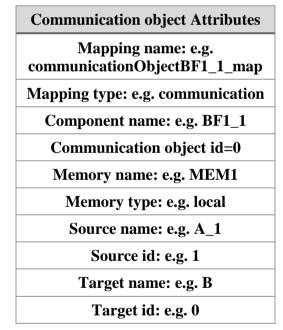

TS specifies the communication objects and their attributes in order to assist the technique selection process (e.g. if memory type==local, use pthreads) while also assigning specific attributes to the PHANTOM protocols and APIs, used inside the components' source code (e.g. queue\_get(var, var->source=2...). The considered communication object attributes are provided in the following table:

Similar to the component attributes, the communication object attributes are the mapping name, relative to the name of the communication object, the mapping type which in this case it is "communication" the component name referring to the communication objects name and the id of the object. In addition, TS considers the physical memory's name (or channel/buffer) to which the communication object is mapped, along with its type (local or shared). Furthermore, TS needs to know the source component name along with its "Source-id" and the target name along with the "Target-id".

The second step includes the parsing of components' source code, in order to specify the attributes of the variables that have to be processed (e.g. sent/received) through the PHANTOM functions. This operation identifies the following attributes:

- 1. The variables to be pushed in queues or memories (e.g. #pragma phantom queue out | output\_image\_L |)

- 2. The variable's attributes: type, dimensions, size (e.g. double | output\_image\_L | [64] |)

- 3. Identification of communication protocols inside the components (e.g. phantom\_queue\_put(...))

In the third step, TS decides on the specific low-level communication API for each component (e.g. components A and B will use MPI but component C will use CUDA). The selection process iterates through the communication objects, where for each of them identifies the source (and target components) and selects the appropriate low-level communication API according to the communication type (e.g. memory/Ethernet), source processor type, target processor type. The following listing provides an example of a low-level communication API indication:

```

If (source processor type == CPU) and (target processor type == CPU) and (communication

type == local memory)

{

return phantom_Pthreads;

}

```

#### Listing 2-1: Example of low level communication API

The current version of TS considers the pthreads, OpenMP, MPI, CUDA, OpenCL APIs (also described in D4.1) for the low-level communication APIs.

The final step includes the attribute replacement and code generation inside the components' source code but also in PHANTOM API headers and functions. In this direction, TS parses the PHANTOM API header files and replaces component-specific attributes with all the information derived from XML and components' code parsing, in order to provide the PHANTOM API communication functions and protocols, with appropriate information, regarding their low-level implementation. The following listing provides an example where pthreads, OMP and MPI specific attributes were added to the component.

//Communication objects IDs and features

#define PHANTOM\_NUMOFCOMMS 2

static int phantom\_source\_id[PHANTOM\_NUMOFCOMMS]={1,2};

//The direction of the communication object: 0.IN-pull, 1.OUT-push, 2.INOUT-both/update

static int phantom\_direction[PHANTOM\_NUMOFCOMMS]={0,1};

//number of components that use a relevant toolkit

#define PHANTOM\_PTHREADS\_COMPS 3

#define PHANTOM\_OMP\_COMPS 0

#define PHANTOM\_MPI\_COMPS 0

#### Listing 2-2: Sample of component attributes definitions

The above information is stored in specific structures initialized at the execution of the PHANTOM application and is used for the proper parallelization of the components and the proper execution of the PHANTOM API functions. The following listing shows an example of a structure to store this information.

struct phantom\_componentlist

{

int id;

int dev\_prc\_type;

int ext\_api;

int cmpprocess; //The process/processor in which the component belongs

int cmp\_slice\_size;

int cmp\_offset;

#### Listing 2-3: Example of PHANTOM API structure

Finally, the existing communication protocol annotations (e.g. phantom\_queue\_put (data...)), are replaced by low-level communication directives (e.g. cudamemcpy (data...)), that indicate the Deployment Manager to generate or activate the actual parallelization functions. TS replaces the arguments of the PHANTOM API functions with the specific communication object attributes, in order to match the function with the appropriate structure corresponding to the variable (e.g. output\_image\_L) and derive its attributes (e.g. source, target, type...). For GPU code implementation, specific low-level commands are considered in order to be generated inside the components' code, used to forward the variables and the functions to the GPU device (e.g. cudaMemcpyAsync(dev\_in, simage, size\_in\*sizeof(double), cudaMemcpyHostToDevice, stream[cmpid]);).

### 2.3.3 Dependencies/integration

TS first interacts with the PHANTOM Repository from where it retrieves its input documents and source code. The first part of the input, consists of the Component Network and the components' source code. TS also interacts with the Multi-Objective Mapper in order to receive its outcome, defined as the optimized deployment plan. TS uses the PHANTOM APIs to select, generate or replace the high-level communication

APIs with appropriate low-level communication APIs and indications. Finally, TS sends the parallelized components to the Deployment Manager for further annotation replacement, code and metadata generation.

# 2.3.4 Demonstration/Example usage

TS decides on the best low-level communication API per component, but it also matches the final deployment plan with the components and their communication functions. In addition, TS replaces existing annotations and information with low-level annotations referring to low-level communication APIs, facilitating the final deployment of the parallelized components. In this direction, the current version is evaluated in terms of its ability to select the appropriate low-level communication API, according to the MOM outcome but also in terms of appropriate annotation replacement.

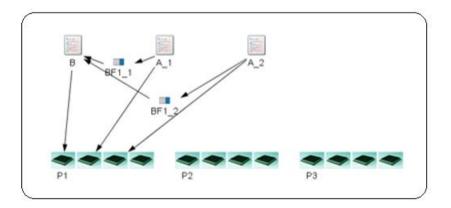

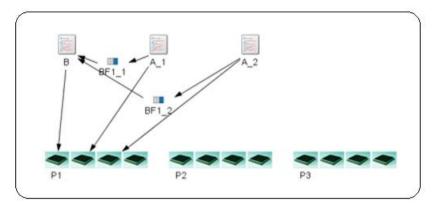

The following paragraph includes an evaluation scenario in which MOM has decided to map three components of an example application to the same processor, on nearby CPUs to avoid the communication overhead. Technique Selection is expected to:

- 1. Identify the interacting components to provide PHANTOM APIs with relative information (annotation replacement and generation) about the component's number and the source and target of the communication objects;

- 2. Select an API that will introduce minimal communication overhead such as OpenMP or pthreads; and

- 3. Generate appropriate low-level communication APIs.

The following figure depicts a diagram that includes the MOM outcome with its components and memories' mapping.

Figure 2-11: Mapping example for Technique selection demonstration

Since the components (in this case A\_1, A\_2, B) are mapped to the same processor and the communication objects (in this case BF1\_1 and BF1\_2) are mapped on two local memories, TS decides (based on the processor type and the type of the communication type) that each component will run on a different thread using pthreads. To this purpose,

TS generates the appropriate values and files in the PHANTOM API functions and communication protocols, as exemplified below:

#define PHANTOM\_PTHREADS\_COMPS 3

#define PHANTOM\_NUMOFCOMPS 3

static int phantom\_source\_id[PHANTOM\_NUMOFCOMMS]={1,2}; static int phantom\_target\_id[PHANTOM\_NUMOFCOMMS]={0,0}; static int phantom\_memtypemat[PHANTOM\_NUMOFCOMMS]={phantom\_localmem,phantom\_loc almem};

Listing 2-4: Techniques selection attributes specification and replacement

In addition TS parses components for phantom\_synchronize() functions and adds the communication object ID in order to use its attributes (source, target, low level communication API, etc.) for the low level protocols activation:

Listing 2-5: Techniques Selection annotations replacement with low level communication API directives

# 2.3.5 Innovations beyond the state-of-the-art

# 2.3.5.1 Background technologies utilised in development XML Parsing Classes

Like the Code Analysis, the Technique Selection is a set of classes and functions implemented in Java, using appropriate XML libraries to parse and modify XML documents. These libraries are mainly required to process the Component Network, that provides all necessary information about the components, and the mapping that is provided by the MOM.

# 2.3.5.2 Summary of new technologies/extensions developed

Technique Selection was fully custom made and is responsible to choose the communication technology to be used for the communication between the different code components. The main part concentrates on extracting all the information relevant to the communication objects from the component network and the mapping provided by MOM, as well as feeding this in the header files that are going to be used for the application's implementation by the Deployment Manager. Based on these header files,

the selection of a suitable communication library is performed to determine the best communication API (OpenMP, MPI, CUDA, OpenCL) that will be used in the deployment phase.

# 2.3.5.3 Early/Full Prototypes functionality Early-First Year Prototype

Technique Selection is able to analyse the component network and the mapping of the code components, in regard to the successful choice among the various communication APIs.

# **Full Prototype and Next Steps**

The fully developed TS will be able to insert lower level annotations, according to the chosen API, for guiding the Deployment Manager to implement (in code) the communication interfaces. A more complex and flexible algorithm will be used for determining the best-suited library for the components' communication needs.

# 2.4 FPGAs

The final supported technique is component parallelisation and acceleration through the use of FPGAs. The focus of the chosen approach is to ensure that modular compilation can be supported by the PHANTOM platform, and that non-FPGA experts can effectively exploit FPGAs that are present in the target architecture.

Creating FPGA designs is difficult, and requires the effort of a skilled hardware designer. It is not yet currently possible to automatically generate high-quality FPGA hardware from a software-based input, however, considerable work is being done in this area. The Xilinx SDAccel [6] development environment attempts to map GPGPU-style programs to FPGA designs, specifically transforming OpenCL programs. SDAccel does not vet target Zynq devices, only FPGA hardware designs are created without accompanying software. Zyng support is in development but not yet released. Similarly, Altera/Intel are developing support for transforming OpenCL programs to their FPGA systems. In both of these cases, the designed hardware is heavily restricted by the OpenCL programming model, and the created designs are very similar to GPGPU-style implementations. This is very effective for some algorithms, but a poor choice for others. FPGA design experts are required to operate this software, because whilst they automate some aspects of the design work, software to hardware high-level synthesis is still in its infancy, and general C/C++ code translates rather poorly. It is necessary to develop code specifically targeted for high-level synthesis rather than expecting it to translate normal software projects to FPGA designs. These tools should be therefore viewed as tools to improve the effectiveness of FPGA experts, rather than to allow nonexperts to use FPGAs.

The PHANTOM project does not attempt to repeat these efforts and aims to allow their use as they become commercially-available. Instead, whilst the commercial tools catch up in these areas, and in order to promote the use of FPGA platforms by non-experts, custom IP cores will be developed manually for the Use Cases and an IP core marketplace feature is developed. These IP cores ascribe to a common set of interfaces defined in this project, and so allow the the PHANTOM platform to automatically integrate varying sets of IP cores into new FPGA designs, thereby supporting a wide range of different target FGPAs.

The PHANTOM platform supports acceleration on Xilinx Zynq FPGAs [5]. The Zynq System on Chip is a multicore ARM device with a closely-coupled FPGA. This allows standard ARM software (such as Linux) to run on the CPUs whilst custom hardware executes within the reconfigurable logic. This means that for the purpose of the PHANTOM project, an FPGA target is a multicore CPU with attached accelerator, the same computation model as is used for the GPU target. An accelerated PHANTOM component consists of not just an IP core, but the ARM software that reads its data and processes the results.

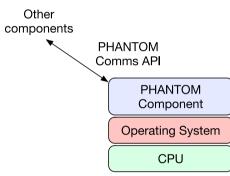

In order to ensure that modular compilation of FPGA components is possible, it is necessary to ensure that any interfaces for hardware and software are defined. These are shown in Figure 2-12.

a) A standard PHANTOM software component

b) A PHANTOM component accelerated on a Zynq FPGA

### Figure 2-12: The interfaces in the PHANTOM FPGA architecture

There are two very low-level interfaces, which ideally would remain invisible to the end user. Currently they must be exposed because automatic transformation to FPGAs is not yet available and must be performed manually. The PHANTOM IP API is used by the software part of the IP which is still executing on the ARM core. This API is used to query the IP cores that are present on the FPGA, start and stop their execution, and to pass data to and from them. This API is a Linux userland API and is part of the Open Source release [7]. The current version of the API can be found at https://github.com/PHANTOM-Platform/PHANTOM-FPGA-Linux/tree/master/API.

The PHANTOM IP Hardware Interface defines the physical connections (wires) that a valid IP core may include to be part of a valid design. This is described in the following section.

# 2.4.1 PHANTOM Hardware Interface

It is often the case that multiple IP cores are to be hosted on the same physical FPGA. For example, if multiple components have hardware implementations, the Multi-Objective Mapper may choose to combine two or more IP cores. The platform therefore must be able to automatically combine IP cores into a single FPGA design. It can do this because IP cores are only allowed to have the following interfaces:

- One clock input. All IP cores run from the same system clock.

- One active-high reset line. This can be asserted by software running on the ARM cores to reset the IP core.

- One active-high interrupt line. This is used by the IP core to signal the ARM cores.

- One AXI Slave interface. This is a standard peripheral interface which allows for low-speed communications between the Linux kernel running on the ARM CPUs and the IP core.

- Between 0-4 AXI Master interfaces. This is a high-speed interface which allows the IP core to read and write main system memory. This is useful for moving data at high speed into and out of the IP core.

These interfaces are all standard, and follow the exact same format as IP cores generated from Xilinx's own software. The software which combines IP cores into a single architecture is part of the Linux software distribution. See its documentation for further details.

# 2.4.2 Innovations beyond the state-of-the-art

### 2.4.2.1 Background technologies utilised in development

The IP cores developed make initial use of the FPGA vendor high-level synthesis tools (Xilinx Vivado HLS) for hardware generation, but the base output is very inefficient so significant modifications must be made to create an effective implementation.

That was the case of the development of the DWT (Discrete Wavelet Transform) IP Core, which started by a generic C implementation as the input of Xilinx Vivado HLS. Despite being generated a useable IP core, the performance was sub-par, so some optimizations were needed to take fully-advantage of the usage of FPGA.

Taking the following table in consideration, it is possible to observe the magnitude of optimization possible to be achieved by having a hardware engineer performing the optimisation of the IP Core.

| Design | Pixels    | Time (s) | Time/pixel<br>(ns) |

|--------|-----------|----------|--------------------|

| 1      | 3686400   | 4.121374 | 1118               |

| 2      | 3686400   | 0.622383 | 169                |

| 3      | 3686400   | 0.548814 | 149                |

| 4      | 3686400   | 0.519238 | 141                |

| 5      | 3686400   | 0.469334 | 127                |

| 6      | 3686400   | 0.288320 | 78                 |

| 7      | 3686400   | 0.289161 | 78                 |

| 8      | 3686400   | 0.252271 | 68                 |

| 9      | 58982400  | 2.991100 | 51                 |

| 9      | 132710400 | 6.726555 | 51                 |

| 10     | 132710400 | 5.56222  | 42                 |

| 12     | 58982400  | 0.813501 | 14                 |

| 13     | 132710400 | 1.188941 | 9                  |

| 14     | 235929600 | 1.477583 | 6                  |

| 15     | 235929600 | 1.187663 | 5                  |

This shows, the poor performance of the direct generation of IP cores by Vivado HLS. And despite that human optimization not being a goal of the project, it clearly shows the level of optimization that is possible to be achieved.

# 2.4.2.2 Summary of new technologies/extensions developed

Due to the inefficiency of vendor high-level synthesis tools, it was necessary to develop interfaces to allow for modular FPGA composition of hardware components. 'PHANTOM IP Cores' were defined, which are IP cores that conform to the following developed interfaces:

- A hardware interface which specifies the I/O for the IP core, including the bus connections, and issues such as memory spaces, interrupts, and clock signals.

- A software interface which specifies how userland software in the PHANTOM Linux distribution can interact with the IP core.

By conforming to these interfaces, the FPGA infrastructure described in D4.2 can automatically create FPGA designs by integrating multiple PHANTOM IP cores, without the developer having to use the FPGA vendor tools, or even to necessarily know that the FPGAs are being targeted. This gives the platform the freedom to explore different hardware mappings of components, as long as a suitable IP core exists. Also, the use of a consistent interface ensures that once vendor high-level synthesis tools are sufficient for truly automatic use, they can be seamlessly integrated into the platform to auto-generate IP cores.

This created an additional step, and a challenge in the development of IP Cores, which is the usage of PHANTOM interfaces. Which implies going from the typical approach of FPGA/Linux integration which focus in AMBA (Advanced Microcontroller Bus Architecture), to FPGA IP cores integration with Linux via Userspace I/O.

# 2.4.2.3 Early/Full Prototypes functionality Early-First Year Prototype

- The IP core interfaces are defined and released.

- As described in deliverable D4.2, the PHANTOM platform includes an implementation of the required hardware to software interface libraries, and of the PHANTOM communications libraries to ensure that components can communicate with the rest of the system.

- The platform also implements the automatic generation of hardware designs from a list of PHANTOM IP cores.

### **Full Prototype and Next Steps**

- Addition of more data movement primitives to the IP core software API to more easily support efficient DMA.

- Further integration of hardware features related to security and additional monitoring.

- Experiment with integration of vendor high-level synthesis tools (Xilinx Vivado HLS) of the possibility to automatic generate (even with low performance) PHANTOM compatible IP Cores.

# **3. PROGRAMMING INTERFACES**

The programming interfaces assist the development of component-based applications, include specific directives about parallelization, and describe functional and non-functional requirements. The provided APIs use the C programming language, enabling the incorporation of parallelization APIs (such as pthreads, OpenMPI, also described in D4.1), whilst also providing an abstraction of the system architecture, hiding the complexity between hardware and applications. Furthermore, the programming interfaces will use the PHANTOM directives defined in D1.2 to forward the user-defined functional and non-functional requirements to the implemented API functionalities. The deliverable D1.2 includes an initial description of the APIs and protocols that will be used in the context of PHANTOM, whilst more protocols and APIs may be useful to be considered in the next steps of the API's implementation.

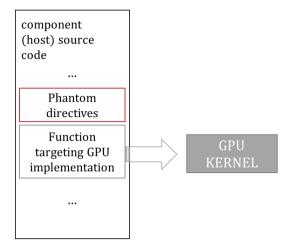

The first version of the programming interfaces is focused on the design and implementation of communication API functions for CPU and GPU platforms in relation to code analysis and transformation operations developed in Section 2.2.5.1. Specifically, the considered APIs are the following (defined in D1.2):

- Shared API (e.g. size\_t phantom\_slice\_size(void \*item);) for manipulating data in the shared memory

- Queue API (e.g. bool phantom\_queue\_get(void \*queue);) for manipulating blocking FIFO data items in mainly distributed memories

- Signal API (e.g. bool phantom\_notify(void \*signal);) for coordination and execution of other components, without sharing any data

The low-level APIs that are considered by the above functions are the pthreads, OpenMP, OpenMPI regarding CPU-CPU communication and CUDA regarding CPU-GPU communication (see D4.1 for details). The design and implementation of the APIs will be continuously refined and modified towards the Use Case requirements along with the progress of the development process. To this purpose, the final implementation of the APIs will be provided at the next deliverable of WP3, along with the rest of the APIs, defined in D1.2.

# **3.1** USE CASE REQUIREMENTS

The programming interfaces are applied in all three PHANTOM Use Cases, which will include them accordingly to the proposed Use Case applications, in order to provide the development process with appropriate functionalities, for components' parallelization and communication among the underlying heterogeneous infrastructure. In this direction, all PHANTOM Use cases will require:

| Req. No. | Requirement                                                                                                                                 | <b>Overall Priority</b> |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| U5       | Support for multi-threaded concurrent tasks, including communica-<br>tion and synchronisation                                               | SHALL                   |

| U7       | Support for communications data-centric applications (e.g. automat-<br>ic scaling of components to the actual size of data to be processed) | SHALL                   |

| U8       | Support for component-based application design                                                                                              | SHALL                   |

| U19 | Generation of target dependent parallel code for all mandatory<br>target platforms without user involvement when sufficient annota- | SHALL |

|-----|-------------------------------------------------------------------------------------------------------------------------------------|-------|

|     | tions are provided.                                                                                                                 |       |

| U20 | Provision of constructs or abstractions to deal with non-uniform and<br>uniform memory, hiding the underlying data transfer details | SHALL |

| U21 | Automation of the process of transferring data to/from different memories according to the component data model                     | SHALL |

| U24 | Provision of means for the developer to describe the composition of<br>hardware components and interactions for the target platform | SHALL |

| U28 | Provision of a data model for specification of input and output data                                                                | SHALL |

| U32 | Support for application source code developed in C                                                                                  | SHALL |

| U33 | Support for higher level language such as Java and C++                                                                              | MAY   |

| U47 | Support for Telecom specific application classes where domain-<br>specific libraries are commonly utilised                          | SHALL |

| U86 | Support for application specific communication bus/protocols                                                                        | MAY   |

# **3.2 SHARED MEMORY API**

### **3.2.1** Design Specifications

The shared API consists of functions for manipulating data stored in the shared memory. As described in D1.2 PHANTOM provides the user with the ability to declare a variable as shared via the appropriate phantom directive (i.e. #pragma phantom shared etc.). Since PHANTOM does not provide automatic consistency, the developer must call synchronization functions in order to update the shared variable in its latter status. For this purpose, PHANTOM provides the following function:

bool phantom synchronize(void \*item);(1)

which causes the local view of the shared memory to be updated.

Furthermore, in case a component, along with its shared data, is parallelized in slices by the Multi-Objective Mapper, PHANTOM provides the following function:

size t phantom slice size(void \*item); (2)

able to return the size (in elements) of the slice allocated to this component. This function, when combined with the appropriate offset, can provide the data processing (e.g. iteration) only between the targeted offset and the returned slice size.

### **3.2.2** Implementation Details

The main functionality of the Shared API is focused on the "synchronize" function which is automatically implemented, according to the MOM's optimized deployment plan and the Parallelization Toolset's Technique Selection. The selected API implementation is then generated (or activated) by the Deployment Manager according to the selected low-level API and the processor's type to which the component is mapped (e.g. since the component with id=0 has phantom\_Pthreads indication and its processor type is CPU, the Deployment Manager will generate (or activate) the function that executes mutex\_lock(), update of shared variable and mutex unlock).

The first version of the synchronization function is provided in the following form:

```

bool phantom_synchronize(void **item, int phantom_cmpid,

int phantom commid) (3)

```

Which includes the following inputs:

- item: the variable to be updated;

- phantom\_cmpid: is the id of the current component. Used for lower-level API generation/activation. Not modifiable by user or Phantom;

- phantom\_commid: is the id of communication object. Technique selection will replace it with actual value.

The following listing provides a first representation of the actual implementation, without details, since this form may change and be refined according to the PHANTOM development process:

```

if (((ext_api == phantom_Pthreads))&&(( dev_prc_type == PHANTOM_CPUSYS)))

{

pthread_mutex_lock(&phantom_pth_ready_mutex);

//Update - global variable

phantom_threadupdate_sync(item, phantom_cmpid, phantom_commid);

pthread_mutex_unlock(&phantom_pth_ready_mutex);

ł

else if (((ext_api == phantom_OpenMP))&&(( dev_prc_type ==

PHANTOM_CPUSYS)))

ł

#pragma omp critical

//Update - global variable

phantom_threadupdate_sync(item, phantom_cmpid, phantom_commid);

//printf("phantom OpenMP\n");

}

else if (((ext_api == phantom_MPI))&&(( dev_prc_type == PHANTOM_CPUSYS)))

MPI_Allgather(&item, comprsize, MPItype, &memvar, comprsize, MPItype,

MPI_COMM_WORLD);

//printf("phantom MPI\n");

ł

```

Listing 3-1: First representation of PHANTOM synchronize function

Furthermore, Shared API includes the function that returns the components' slice size and is currently implemented in the following form:

```

size_t phantom_slice_size(int compid); (4)

```

The input of the function is the id of the component that is sliced. It is assumed that the Parallelization Toolset's Techniques selection created specific variables that hold information such as component's communication API and component's slice size. The latter is called inside the phantom\_slice\_size() (e.g. temp\_slice\_size = phantom\_compx[cnum]->cmp\_slice\_size ) which then returns the component's size.

# 3.3 QUEUE API

# **3.3.1** Design Specifications

The Queue API offers the appropriate facilities that enable the user to manage the communication between components that are mainly mapped to distributed memories and are linked with specific communication objects in the form of queues. Specifically, these queues have the form of blocking FIFOs of arbitrary size (see D1.2). The functions of the Queue API provide the user with the ability to send or receive elements and to count the number or size of the elements which are in the queue. The Queue API functions addressed in the current stage are the following:

```

bool phantom queue get(void *queue); (5)

```

Used for pulling items from the queue:

```

bool phantom_queue_put(void *queue, void *item); (6)

```

Used for adding items to the queue:

uint32 t phantom queue count(void \*queue); (7)

Used for counting the number of items currently in the queue:

# **3.3.2** Implementation Details

The implementation of the Queue API includes low-level communication APIs targeting mappings of components to platforms with distributed physical memories, while also considering functions able to handle thread-based APIs in case of mapping to shared physical memories. The implementation of the Queue API functions changes automatically, according to the platform that the communication is mapped. For example, when components are mapped to different devices, they will have to use a communication API supporting communication between distributed memories, such as MPI, while in case the components are mapped in the same device, components could use a low-overhead thread-based API such as pthreads (see D4.1 for further information). The actual implementation of the functions is decided by the PT's Technique Selection, using MOM's outcome and generated by the Deployment Manager. The following paragraphs describe the first implementation of the Queue API functions:

The function that is used to get data from a receiving queue is declared as follows:

The inputs of the function are the following:

- Queue: The variable/ array/ structure to be retrieved from the received queue

- phantom\_cmpid: id of the component that calls the function.

- phantom\_commid: id of communication object (in relation to the optimized deployment plan).

The first sample of the implementation is provided in the following listing, skipping details from custom source code, since this form may change and refined according to the PHANTOM development process:

```

if ((ext_api == phantom_Pthreads))&&(( dev_prc_type == PHANTOM_CPUSYS)))

{

errlock = pthread_mutex_lock(&phantom_pth_ready_mutex);

//update queue

phantom_threadupdate_get(queue, phantom_cmpid, phantom_commid);

errlock = pthread_mutex_unlock(&phantom_pth_ready_mutex);

}

else if (((ext_api == phantom_OpenMP))&&(( dev_prc_type == PHANTOM_CPUSYS))))

{

#pragma omp critical

{

phantom_threadupdate_get(queue, phantom_cmpid, phantom_commid);

}

}

else if (((ext_api == phantom_MPI))&&(( dev_prc_type == PHANTOM_CPUSYS))))

{

MPI_Status phantom_mpi_status;

MPI_Recv(&queue, comprsize, MPItype, src_id, phantom_commid,

MPI_COMM_WORLD, &phantom_mpi_status);

}

```

Listing 3-2: First representation of PHANTOM queue get functionality

As depicted in the above listing, in case the component with id=1 has phantom\_MPI indication and its processor type is CPU, the Deployment Manager will activate or replace the phantom\_queue\_get with the corresponding MPI\_Recv(...) function to receive the specified variable.

Similarly, the function to put data, to be sent over a queue is declared as follows:

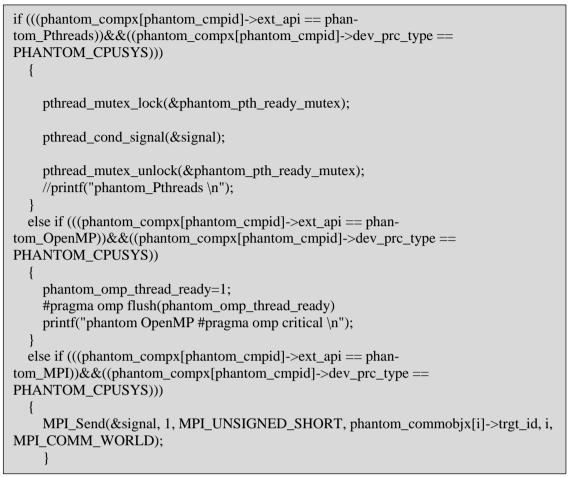

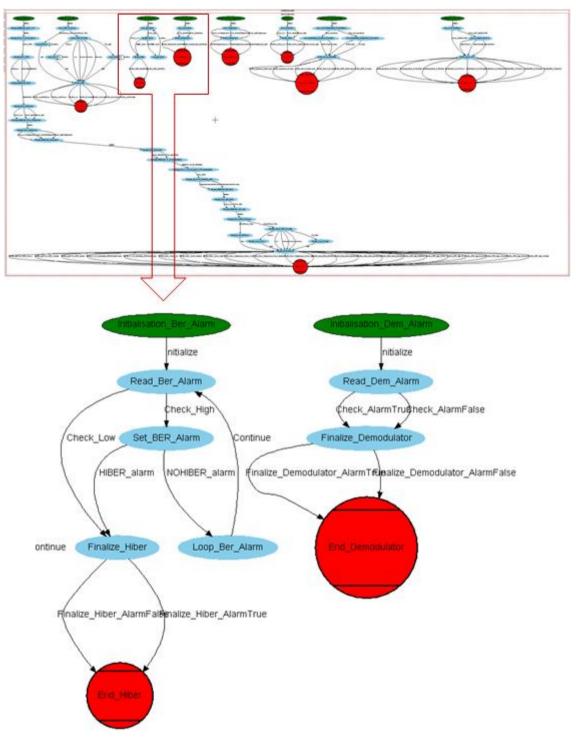

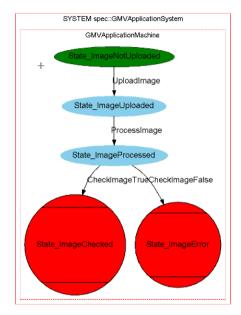

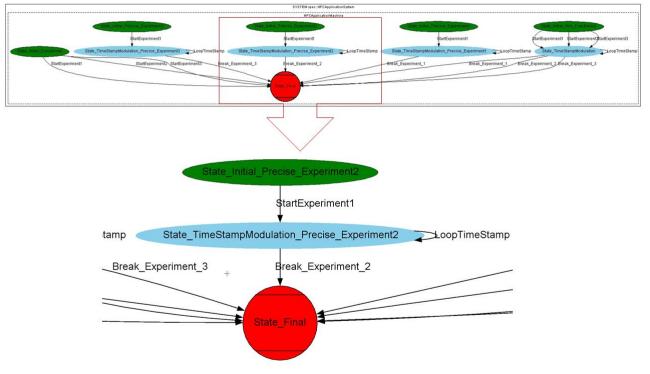

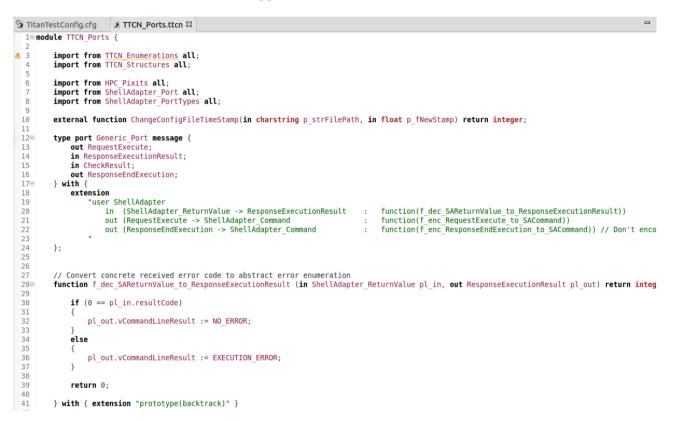

The phantom\_queue\_put() is implemented in a similar manner, where instead of thread\_get and MPI\_Recv functionalities, the queue\_put is using thread\_put and MPI\_Send functions.